概要

説明

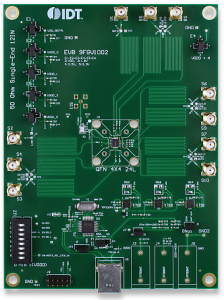

The 9FGV1002 is a member of Renesas' PhiClock™ programmable clock generator family. The 9FGV1002 provides four spread-spectrum copies of a single output frequency and two copies of the crystal reference input. Two select pins allow for hardware selection of the desired configuration, or two I²C bits all easy software selection of the desired configuration. The user may configure any one of the four OTP configurations as the default when operating in I²C mode. Four unique I²C addresses are available, allowing easy I²C access to multiple components.

特長

- PCIe Gen1–7 compliant

- PCIe Gen7 Common Clock jitter < 41fs RMS

- 276fs RMS typical phase jitter at 156.25MHz (12kHz–20MHz)

- 4 programmable output pairs plus 2 LVCMOS REF outputs

- 1 integer, fractional or spread-spectrum output frequency per configuration

- 1MHz–325MHz output frequency (LVDS or LP-HCSL)

- 1MHz–200MHz output frequency (LVCMOS)

- 1.8V to 3.3V core VDD

- Individual 1.8V, 2.5V or 3.3V VDDO for each programmable output pair

- Supports HCSL, LVDS and LVCMOS I/O standards

- Supports AC-coupled LVPECL and CML logic – see AN-891

- 4 × 4 mm 24-VFQFPN and 24-LGA packages with 50MHz integrated crystal option

- Supported by Timing Commander™ software

製品比較

アプリケーション

設計・開発

製品選択

適用されたフィルター

ビデオ&トレーニング

Ron Wade, chief PCIe system architect explains the fundamental difference in reference clock jitter budgets between the first three generations of the specification and those of Gen4 and Gen5 which raise new challenges for designers.

Related Resources