組込機器でのAIモデル実装に難しさを感じていることはないでしょうか?

AIモデル実装を簡単にするDRP-AI TVM[1]をご紹介します。

近年、監視カメラ、交通監視システム、ロボット、ドローン等の組込機器へのAI実装が進んでおります。組込機器はクラウド環境と異なり、HW性能、コストや電力制限等 考慮すべきことが多いというAI実装の難しさがあります。ルネサスの低消費電力AIアクセラレータ DRP-AIを実装したAI-MPU RZ/Vシリーズを活用いただくことで、HWに関する実装課題の大部分は解消されます。

お客様がAIモデルを当社AI-MPUへ実装する際、AIモデルをDRP-AIの実行形式へ変換するDRP-AIトランスレータをご使用いただいておりますが、一部のお客様から実装が難しいとのご指摘を頂いております。

その理由は大きく2つあります。

- DRP-AIトランスレータがサポートするAIモデルのフォーマットはONNXのみ

- DRP-AIトランスレータがサポートしていないオペレータが含まれていると変換できない

今までルネサスは、このような場合の対応をお客様ご自身にお願いしておりましたので、一部のお客様にご負担をおかけしておりました。このような課題を解決することでお客様の利便性が向上すると考え、新規にDRP-AI TVMをリリースいたしました。

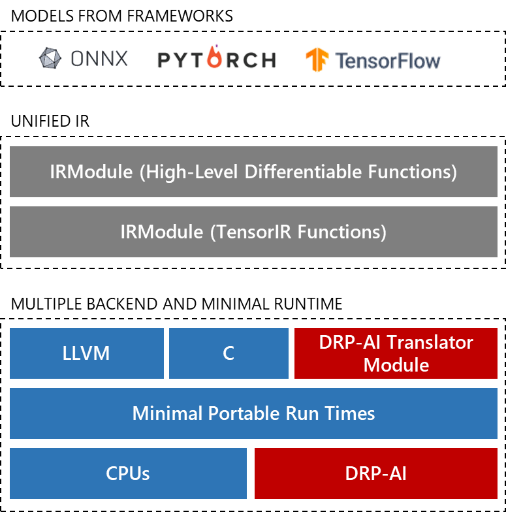

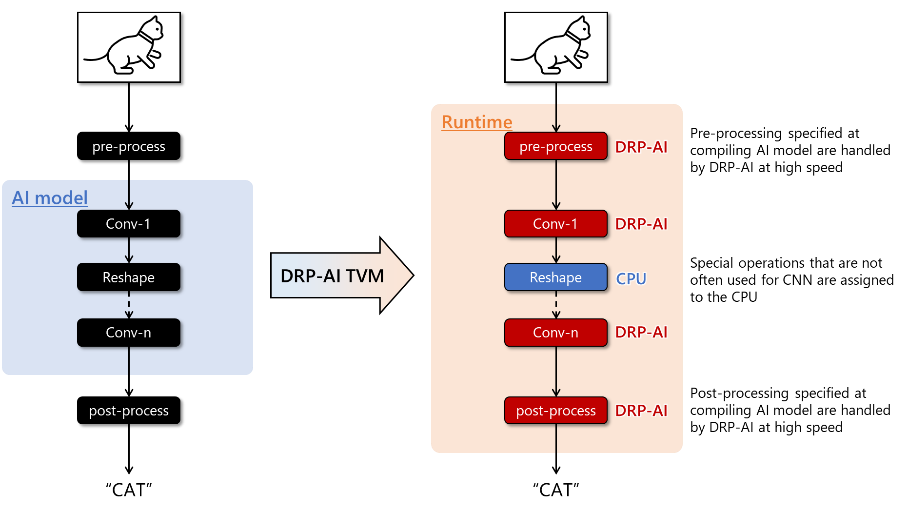

DRP-AI TVMはオープンソースのMLコンパイラであるApache TVMをDRP-AIに対応させたツールです。DRP-AI TVMを使用することで、DRP-AIトランスレータがサポートしていないオペレータを自動的にCPUへ割り振ることができ、簡単により多くのAIモデルに対応できるようになります。またONNX以外のAIフレームワークのフォーマットを扱うことができます。更に、従来のDRP-AIトランスレータでのフローと同様に、AI推論の前処理をDRP-AIで処理できるため、前処理も含んだトータルのAI性能向上が可能です。

DRP-AI TVMの構成

DRP-AI TVMによる、AIモデル オペレータの自動CPU割り振り

DRP-AI TVMはお客様が簡単にアクセス出来る様に、GitHubに公開しております。 このGitHubにはチュートリアル、サンプルコード、各種AIモデルの性能評価結果等、お客様がご使用いただくうえで十分な情報が全てそろっております。チュートリアルには環境の構築からルネサス評価ボードでの推論までの手順が含まれており、お客様はこの手順を参考に、お客様のAIモデルを簡単に評価することができます。 今後もルネサスは、お客様がより簡単にルネサス製品をご活用いただけるようUX改善に努めてまいります。

ご参考:

[1] DRP-AI TVM is powered by EdgeCortix MERA™ Compiler Framework.

[2] 製品紹介リンク

[3] Renesas info wiki RZ/V series

[4] DRP-AI説明ページ

[5] DRP-AI TVM GitHubリンク

[6] DRP-AI TVM Tutorial

[7] EVK購入リンク:

• RZ/V2L Evaluation Board Kit

• RZ/V2M Evaluation Board Kit

• RZ/V2MA Evaluation Board Kit