概要

説明

9FGV1004は、ルネサスのPhiClock™プログラマブルクロックジェネレータファミリのひとつです。 9FGV1004は、整数に関連する2つの周波数が各1コピー、フラクショナルまたはスペクトラム拡散の周波数が2コピー、水晶振動子のリファレンス入力が2コピー用意されています。 2つの選択ピンでハードウェア的に、または2つのI²Cビットでソフトウェア的に、簡単にかつ希望のコンフィギュレーションで選択することができます。 I²Cモードで動作させる場合、ユーザーは4つのOTPコンフィギュレーションから1つをデフォルトとして設定することができます。 4つのユニークI²Cアドレスが利用可能で、複数のコンポーネントに簡単にI²Cアクセスすることができます。

特長

- PCIe Gen1-4準拠

- 156.25MHz(12kHz-20MHz)での267fs RMS標準位相ジッタ

- プログラマブル出力4組+LVCMOS REF出力2組

- 1コンフィギュレーションにつき整数値出力2点、フラクショナル、またはスペクトラム拡散出力1点

- 1MHz~325MHzの整数値出力(LVDSまたはLP-HCSL)

- 1MHz〜200MHzの整数値出力(LVCMOS)

- 1.8V〜3.3Vコア VDD

- プログラマブル出力ペアごとに1.8V~3.3VのVDDOを搭載

- HCSL、LVDS、LVCMOSのI/O規格に対応

- ACカップリングのLVPECLおよびCMLロジックをサポート - AN-891参照

- 50MHz水晶振動子内蔵オプション付き4 × 4mmの24-VFQFPNおよび24-LGAパッケージ

- Timing Commander™ ソフトウェアに対応

製品比較

アプリケーション

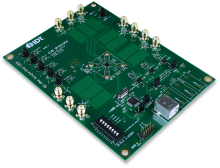

設計・開発

製品選択

適用されたフィルター

ビデオ&トレーニング

PCIe Reference Clock Jitter Budgets

Ron Wade, chief PCIe system architect explains the fundamental difference in reference clock jitter budgets between the first three generations of the specification and those of Gen4 and Gen5 which raise new challenges for designers.

Related Resources

Video List